WEEK 8 LEARNING OBJECTIVES

Day 1

- Describe the basic structure of a memory

array.

- Define address.

- Define data.

- Define address bus.

- Define data bus.

- Define word.

- List the standard JEDEC memory size prefixes

from kilo through Peta.

- Match the standard JEDEC memory size

prefixes with the corresponding power-of-2 memory array depth

depth.

- Draw a simple block diagram of the memory bit cell.

- Draw a simple bloxk diagram of an MxN memory

array.

- Describe the role of the decoder in the MxN

memory array.

- Describe how data is read and written from

an MxN memory array.

- Compare and contrast single

and multi-ported memories.

Day 2

- Compare and contrast

volatile and non-volatile memories.

- Compare and contrast

RAM and ROM memories.

- Compare and contrast

static and dynamic RAM.

- List the five principle types of ROM.

- Compare and contrast

the five principle types of ROM.

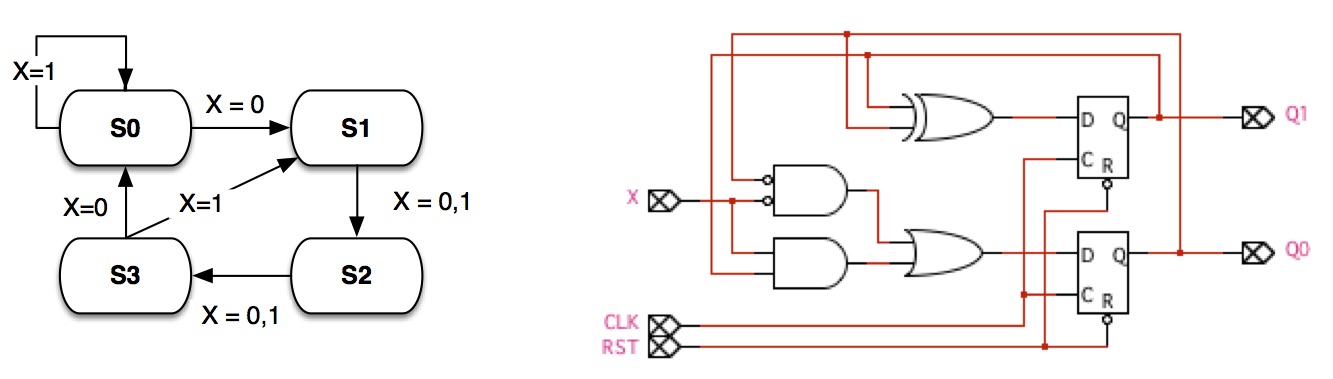

- Use ROM memories to implement look up

tables for the next state and output equations for a FSM.

Day 3

- Define register file.

- Design and simulate

a VHDL register file description.

- Design and simulate

a VHDL SRAM description.

- Design and simulate

a VHDL ROM description.