WEEK 5 LEARNING OBJECTIVES

Day 1

- Define the architectural state of a machine.

- List the items in the ARM architectural

state.

- Compare and contrast the

Princeton and Harvard organizations.

- Define the Princeton bottleneck.

- Describe if modern systems are Princeton

organized, Harvard organized, or both.

- Describe the ARM program counter component.

- Describe the ARM instruction memory ROM.

- Describe the ARM register file component.

- Describe the ARM ALU component.

- Describe the ARM data memory RAM.

- Use the ARM instruction formats to organize

a single-cycle processor.

Day 2

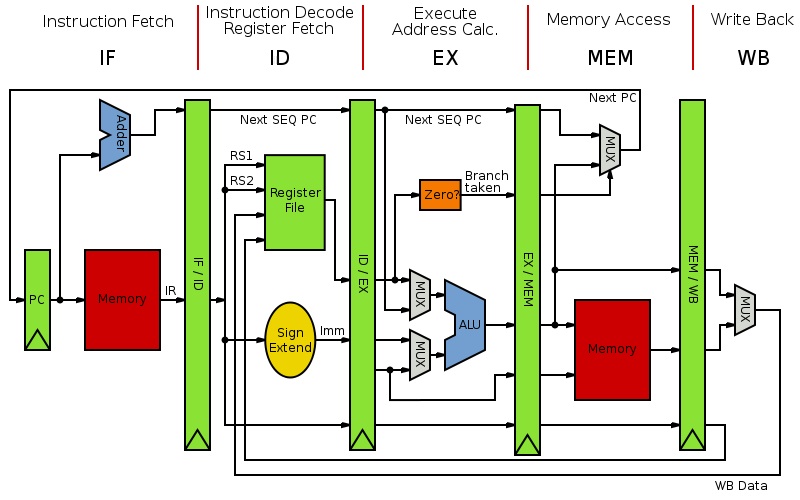

- Draw the ARM single-cycle processor designed

in lecture. Do it again! Practice drawing the blueprint

over and over.

- Write the values of the control signals that

must be generated by the controller of the ARM single-cycle

processor for each implemented instruction.

- State the result of stuck-at faults on ARM

single-cycle processor control signals.

Day 3

- Draw the ARM single-cycle processor designed

in lecture. Do it again! Practice drawing the blueprint

over and over.

- State the ARM instruction that requires the

longest delay.

- Calculate the minimum clock period for an

ARM single-cycle processor given specific component propagation

delays.

- State the execution time equation.

- Use the execution time equation given

instruction specifications.