WEEK 7 LEARNING OBJECTIVES

Day 1

- Describe how pipelined microarchitectures

exploit instruction level parallelism to improve throughput.

- State the number of instructions in flight every

clock cycle when a basic ARM pipelines is full.

- Describe how pipelining improves throughput.

- State the theoretical pipeline speedup (compared to

single-cycle) for a pipeline of length n.

- State why the theoretical pipeline speedup cannot be achieved.

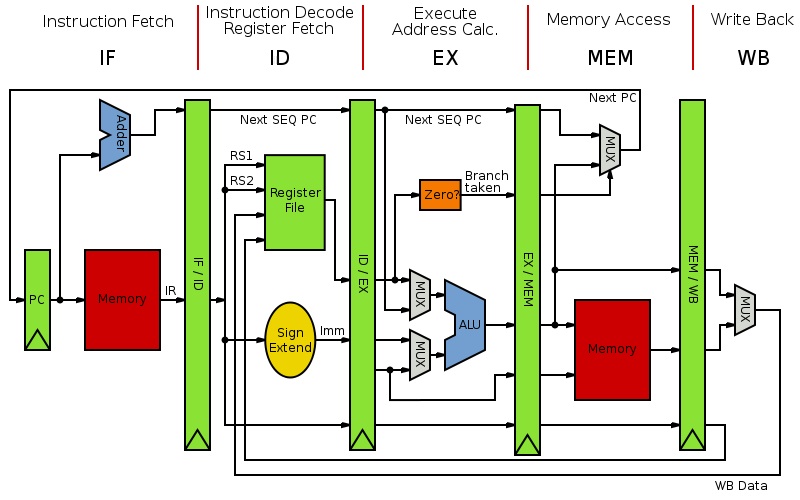

- Describe the use of interstage registers in pipeline

microarchitecture.

- List the five stages of instruction execution in

ARM pipeline microarchitectures.

- Draw an abstract blueprint showing the insertion of

pipeline registers between the stages of ARM instruction execution.

Show the feedback paths for PC update and register

write-back.

- Draw an ARM flight-plan diagram showing in-flight

instructions during pipeline fill and full pipeline execution.

- Justify the statement "Pipeline microarchitectures

make very efficient time usage of components."

Day 2

- List the three types of pipeline hazards.

- List examples of structural hazards.

- State how structural hazards are eliminated when

implementing pipelined microarchitectures.

- Justify the Harvard organization in pipelined

implementations.

- List the two broad categories of data hazards.

- Describe the hazard window for ARM pipeline

microarchitectures if hazard-protection is not implemented.

- Identify load-use and register-use data hazards

in code segments.

- Calculate hazard distances for a given instruction

sequence.

- List the three principal techniques used to remove

data hazards. Describe the advantages and disadvantages

of each technique.

- Describe how the hazard window suggests forwarding

paths for data hazard prevention.

- Draw an abstract blueprint showing the insertion of

pipeline registers between the stages of ARM instruction execution,

the feedback paths for PC update and register write-back, and forwarding

paths for data hazard prevention.

Day 3