DESIGN SOFTWARE AND TUTORIALS

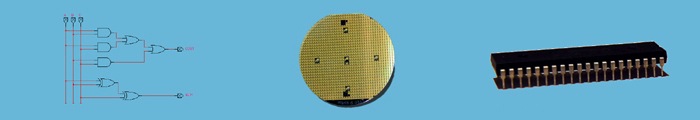

Quartus is electronic design automation (EDA) software from Altera

Corporation. It is used to design and simulate digital logic circuits

using schematic gate and function symbols. Design blocks can also be

described using hardware description languages. An extensive toolset is

provided to simulate the behavior of the circuit, tweak circuit performance,

and to compile the design to a programmable file for placement in one of the

Altera complex programmable logic devices (CPLDs) or field-programmable gate

arrays (FPGAs). A CPLD or FPGA takes the place of many interconnected

components as a single-chip solution to a design problem.

Students in CE1900 will use Quartus extensively.

Follow these steps in

order to install and learn about Quartus.

- Download the Quartus toolset by clicking

and choosing "Save".

- Installation

instructions for the Quartus software.

-

MSOE schematic diagram

entry and simulation tutorial.

-

Altera Schematic diagram entry and simulation tutorial.

-

Use this process to print

simulation results for grading.

Version 9.0 of Quartus is available

here for students

encountering memory errors when running Quartus 13.

Students in CE1900 use the VHDL hardware description language to describe

combinational logic circuits. VHDL is an acronym for

Very High Speed Integrated Circuit

Hardware

Description

Language.

These VHDL examples contain extensive comments

to help students learn the language. The examples should be

read and worked in the order listed

on this page because the VHDL comments build on

each other from one file to the next as students are introduced to new ideas

in VHDL design and synthesis

- ENTITY PRIME written using a

dataflow architecture with and, or, and

not logical assignment to implement a K-map minimized

equation.

- ENTITY PRIME written using a

dataflow architecture with logical assignment implementing a canonical

equation.

- ENTITY PRIME written using a

with-select selected assignment statement.

- ENTITY PRIME written using a

when-else conditional assignment statement.

- ENTITY PRIME written using a

with-select selected assignment statement and bit_vectored inputs.

- ENTITY PRIME written using a

when-else conditional assignment statement and bit_vectored inputs.

- ENTITY FULLADD written using a

logical assignment statements.

- SCHEMATIC RIPPLE-CARRY ADDER used

to illustrate the next few VHDL examples pictorially.

- ENTITY RCA4 written using a

structural architecture to interconnect fulladd components.

- ENTITY RCA8 written using a

structural architecture to interconnect fulladd components.

- ENTITY RCAN written

using a generic width to allow different size adders.

- STYLE GUIDE written to

illustrate the proper style of VHDL comments, entity declarations, and

architecture description indentations that should be used by all students

in the computer engineering courses.