LABORATORY KIT

- This course requires an Altera University Program /

Terasic DE10-Lite development board. This board is purchased

in CE1901. Students that did not take MSOE CE1901 must

purchase the CE1901 kit materials from EECS Technical

Support (S-348).

LABORATORY REFERENCES

PRELABORATORY EXPECTATIONS

- Consult the instructor during office hours for

clarification or help with the assigned laboratory exercises.

- Read the laboratory completely before

begining your work. Weeks 3 through 10 are written as formal

requirements and specifications documents. These documents are

significantly longer than the academic lab handouts from CE1901.

Requirements are things a system must do.

Specifications are how the system does it! These

types of documents are created for most engineering projects.

- Complete the laboratory design and

simulation exercises during the week before the lab is due.

- Add appropriate code documentation comments to

your VHDL code.

- Simulate your solution to verify operation.

- Write a short one-page document that describes

the work completed, your approach to simulation, and how you know the

simulation proves your solution works.

- Study the laboratory material and

prepare to answer questions from the instructor

during your demonstration.

LABORATORY EXPECTATIONS

- Bring your laptop and laboratory board to

every lab.

- Demonstrate your working solution to the

instructor when called upon.

- Submit your one page essay, printed VHDL code,

and simulations as a stapled submission packet.

- Preview the next laboratory exercise.

Prepare questions for the instructor if needed.

- Begin work on the next laboratory exercise.

LABORATORY TEAMWORK

- There are usually no laboratory teams in CE1911. Most labs

will be worked by each individual student.

- Feel free to consult with each other as you work on laboratory

exercises but remember that you are responsible for the course

material and will be quizzed by the instructor during your

demonstration.

LABORATORY TESTING

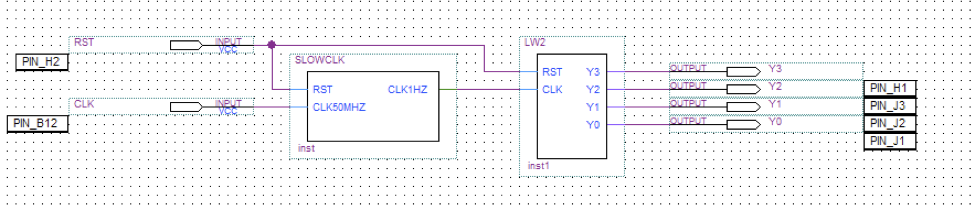

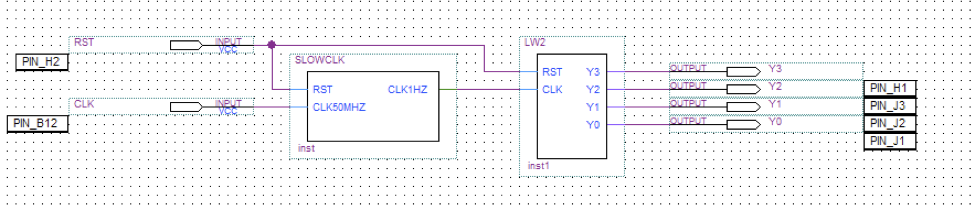

- Many designs in CE1911 will run at high speed. The laboratory

logic analyzers will be used to see these high speed machine outputs.

- Students often want to test their machines at slow speed before

coming to the laboratory period. Use this

VHDL slowclock component inserted

into the clock path to slow down the 50MHz Altera DE0-Nano-SOC

clock to a 1Hz clock. Assign output pins to Altera DE0 LEDs to

watch their behavior at slow speed as shown below.

LABORATORY SCHEDULE